发布日期:2025-02-18 12:05 点击次数:89

咱们都以为 CPU 是计算机的“大脑”,但这究竟意味着什么呢?数十亿个晶体管在计算机里面是如何运作的?在这个由四部分组成的系列著述中,咱们将重心先容计算机硬件假想,先容计算机运行的世代相承。

本系列将涵盖计算机架构、处理器电路假想、VLSI(超大界限集成)、芯片制造以及计算的明天趋势。若是您一直对处理器里面职责旨趣的细节感酷好,请络续存眷 - 这是您初学所需了解的内容。

计算机架构基础

CPU 骨子上作念什么?

让咱们从高等次运行,了解一下处理器的功能以及构建模块如安在功能假想中组合在一谈。这包括处理器中枢、内归档次结构、分支预测等。首先,咱们需要对 CPU 的功能有一个基本界说。

最简便的说明注解是,CPU 恪守一组提醒对一组输入引申某些操作。举例,这可能是从内存中读取一个值,将其添加到另一个值,临了将闭幕存储回内存中的不同位置。它也可能是更复杂的操作,举例若是前一次计算的闭幕大于零,则将两个数字相除。

当你念念要运行一个方法(比如操作系统或游戏)时,方法自身等于一系列供 CPU 引申的提醒。这些提醒从内存中加载,在简便的处理器上,它们会一一引申,直到方法完成。诚然软件开发东谈主员使用 C++ 或 Python 等高级讲话编写方法,但处理器无法领路这些讲话。它只可领路 1 和 0,是以咱们需要一种方法来以这种边幅泄露代码。

CPU 提醒基础常识

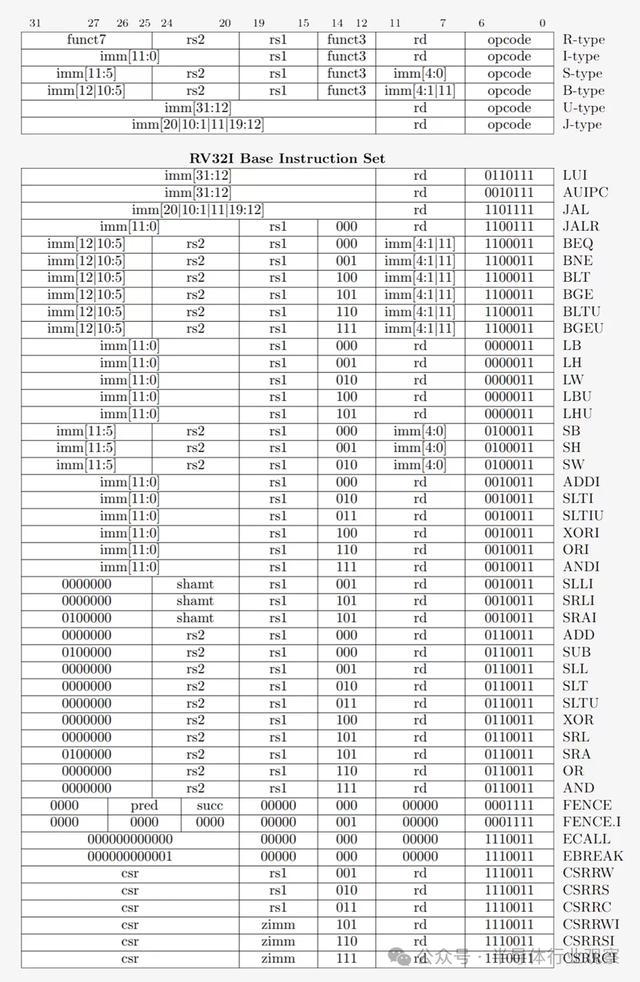

方法被编译成一组初级提醒,称为汇编讲话,是提醒集架构 (ISA) 的一部分。这是 CPU 构建来领路和引申的提醒集。一些最常见的 ISA 是 x86、MIPS、ARM、RISC-V 和 PowerPC。就像用 C++ 编写函数的语法与用 Python 编写引申换取操作的函数不统一样,每个 ISA 都有我方的语法。

这些 ISA 可以分为两大类:固定长度和可变长度。RISC-V ISA 使用固定长度提醒,这意味着每条提醒中一定数目的预界说位数决定了它是哪种类型的提醒。这与使用可变长度提醒的 x86 不同。在 x86 中,提醒可以以不同的样式编码,而况不同部分的位数也不同。由于这种复杂性,x86 CPU 中的提醒解码器常常是通盘假想中最复杂的部分。

固定长度提醒由于其规定结构而更容易解码,但限定了 ISA 可以相沿的提醒总和。诚然 RISC-V 架构的常见版块有大要 100 条提醒而况是开源的,但 x86 是独到的,莫得东谈主真确知谈存在若干条提醒。东谈主们常常以为有几千条 x86 提醒,但实在的数字并不公开。尽管 ISA 之间存在各异,但它们都具有基本换取的中枢功能。

RISC-V 提醒示例。右侧的操作码为 7 位,决定提醒类型。每条提醒还包含要使用哪些寄存器以及要引申哪些功能的位。这等于汇编提醒如何明白为二进制以便 CPU 领路的样式

现在咱们准备翻开电脑并运走时行方法。提醒的引申骨子上有几个基本部分,这些部分通过处理器的多个阶段进行明白。

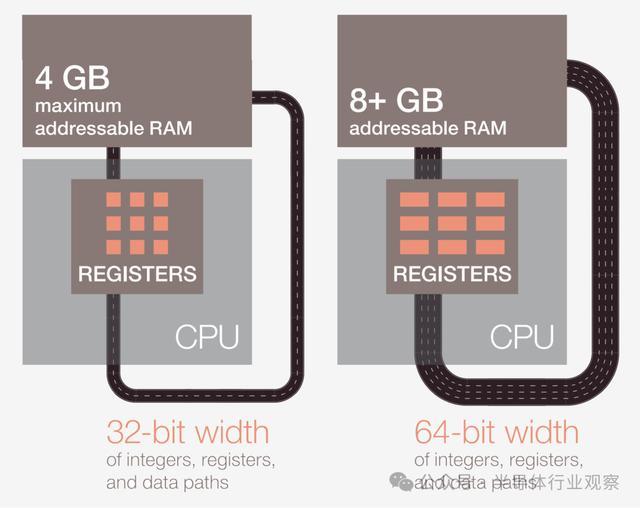

获取、解码、引申:CPU 引申周期

第一步是将提醒从内存中索要到 CPU 中运行引申。第二步,对提醒进行解码,以便 CPU 或者详情它是哪种类型的提醒。提醒有许多种类型,包括算术提醒、分支提醒和内存提醒。一朝 CPU 知谈它正在引申哪种类型的提醒,提醒的操作数就会从内存或 CPU 中的里面寄存器中采集。若是你念念将数字 A 加到数字 B,那么在你真确知谈 A 和 B 的值之前,你无法进行加法。大多数当代处理器都是 64 位的,这意味着每个数据值的大小为 64 位。

64 位是指 CPU 寄存器、数据旅途和/或内存地址的宽度。对于日常用户来说,这意味着一台计算机一次可以处理若干信息,最好将其与架构较小的 32 位进行比较。64 位架构一次可以处理两倍的信息(64 位对 32 位)

CPU 取得提醒的操作数后,将进入引申阶段,在此阶段对输入引申操作。这可以是将数字相加、对数字引申逻辑运算,或者仅仅传递数字而不进行修改。计算闭幕后,可能需要探听内存来存储闭幕,或者 CPU 可以只将值保存在其里面寄存器之一中。存储闭幕后,CPU 将更新各个元素的气象并络续引申下一条提醒。

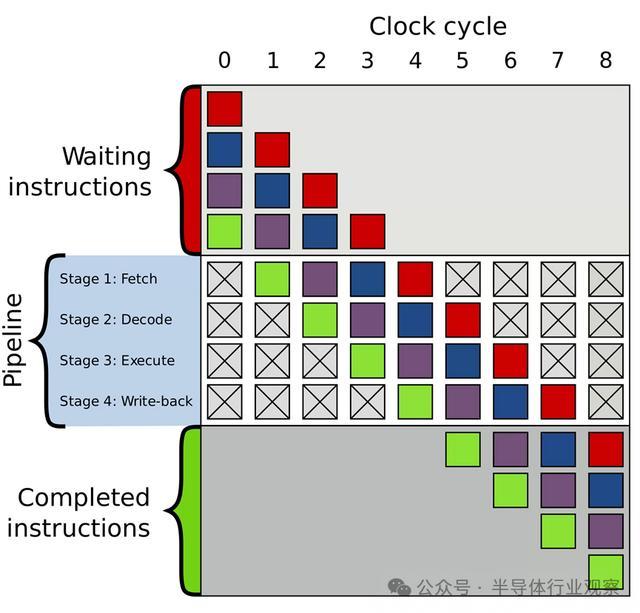

天然,这种刻画是一种极大的简化,大多数当代处理器会将这几个阶段明白为 20 个或更多个较小的阶段,以提高成果。这意味着,尽管处理器每个周期都会启动和完成几条提醒,但任何一条提醒从运行到扫尾可能需要 20 个或更多个周期才略完成。这种模子常常被称为管谈,因为需要一段时分才略填满管谈并让液体都备通过管谈,但一朝填满,就会得到恒定的输出。

4 级活水线示例。彩色框泄露相互零丁的提醒

无序引申和超标量架构

提醒的通盘周期是一个绝顶严实编排的进程,但并非系数提醒都可能同期完成。举例,加法绝顶快,而除法或从内存加载可能需要数百个周期。大多数当代处理器都是乱序引申的,而不是在一条慢速提醒完成时让通盘处理器停滞。

这意味着它们将详情在给定时安分引申哪条提醒最成心,并缓冲其他尚未准备好的提醒。若是刻下提醒尚未准备好,处理器可能会在代码中上前跳转,稽察是否有其他提醒已准备好。

除了无序引申除外,典型的当代处理器还领受所谓的超标量架构。这意味着,在职何时候,处理器都在活水线的每个阶段同期引申许多提醒。它还可能恭候数百条提醒运行引申。为了同期引申许多提醒,处理器里面将领有每个活水线阶段的多个副本。

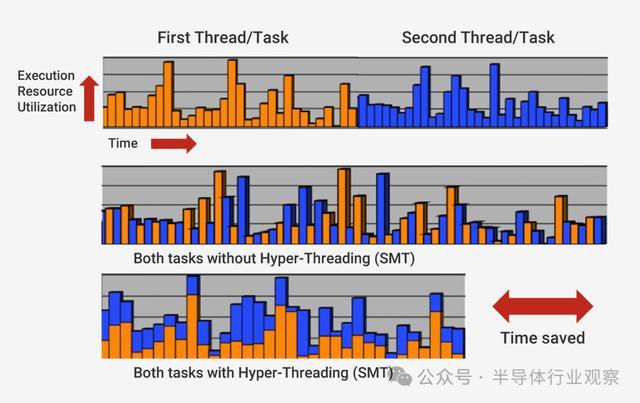

若是处理器发现两条提醒已准备好引申,且它们之间莫得依赖关系,它就会同期引申这两条提醒,而不是恭候它们区别完成。这种作念法的一个常见竣事称为同步多线程 (SMT),也称为超线程。英特尔和 AMD 处理器常常相沿双向 SMT,而 IBM 已开发出相沿多达八路 SMT 的芯片。

为了竣事这种全心编排的引申,处理器除了基本中枢除外还具有许多疏淡元素。处理器中少见百个单独的模块,每个模块都有特定的用途,但咱们只先容基础常识。最大和最有用的两个是缓存和分支预测器。咱们不会先容的其他结构包括从头排序缓冲区、寄存器别号表和保留站等。

缓存:加速内存探听

缓存的用途不时令东谈主困惑,因为它们就像RAM或SSD一样存储数据。关联词,缓存的不同之处在于它们的探听延迟和速率。尽管 RAM 绝顶快,但对于 CPU 来说,它的速率太慢了。RAM 可能需要数百个周期才略反映数据,处理器将无事可作念。若是数据不在 RAM 中,则可能需要数万个周期才略探听 SSD 上的数据。莫得缓存,咱们的处理器将堕入停顿。

处理器常常有三级缓存,形成所谓的内归档次结构。L1 缓存最小且速率最快,L2 缓存居中,L3 缓存最大且速率最慢。档次结构中缓存上方是微型寄存器,用于在计算时间存储单个数据值。这些寄存器是系统中速率最快的存储开辟,速率快了几个数目级。当编译器将高级方法休养为汇编讲话时,它会详情应用这些寄存器的最好样式。

当 CPU 从内存肯求数据时,它首先查验该数据是否已存储在 L1 缓存中。若是是,则只需几个周期即可快速探听数据。若是不存在,CPU 将查验 L2,然后搜索 L3 缓存。缓存的竣事样式常常对内核透明。内核只会在指定的内存地址肯求一些数据,而况档次结构中领有该数据的任何级别都会作念出反映。跟着咱们进入内归档次结构的后续阶段,大小和延迟常常会增多几个数目级。临了,若是 CPU 在职何缓存中都找不到它要查找的数据,那么它才会转到主内存 (RAM)。

在典型的处理器上,每个中枢将有两个 L1 缓存:一个用于数据,一个用于提醒。L1 缓存常常统共约 100 KB,大小可能因芯片和代数而异。每个中枢常常还有一个 L2 缓存,尽管在某些架构中它可能在两个中枢之间分享。L2 缓存常常为几百 KB。临了,有一个 L3 缓存,它由系数中枢分享,大小约为几十兆字节。

当处理器引申代码时,它最常使用的提醒和数据值将被缓存。这权臣加速了引申速率,因为处理器无须不竭进入主内存来获取所需的数据。咱们将在本系列的第二和第三部分中进一步接头这些内存系统的骨子竣事样式。

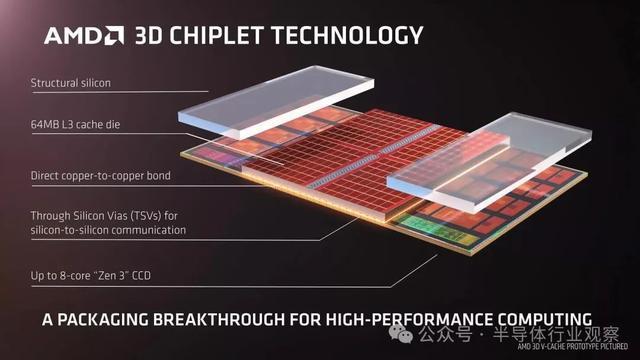

还值得庄重的是,诚然三级缓归档次结构(L1,L2,L3)仍然是程序,但当代 CPU(举例 AMD 的Ryzen 3D V-Cache)也曾运行加入疏淡的堆叠缓存层,这往往会在某些情况下提高性能。

分支预测和推测引申

除了缓存除外,当代处理器的另一个要害构建块是准确的分支预测器。分支提醒雷同于处理器的“if”语句。若是条目为真,则引申一组提醒,若是条目为假,则引申另一组提醒。举例,您可能念念要比较两个数字,若是它们特地,则引申一个函数,若是它们不同,则引申另一个函数。这些分支提醒非不时见,可以占方法中系数提醒的约 20%。

从名义上看,这些分支提醒似乎不是什么问题,但骨子上,它们对于处理器来说绝顶具有挑战性。由于在职何时候,CPU 都可能同期引申十到二十条提醒,因此知谈要引申哪些提醒绝顶迫切。可能需要 5 个周期来详情刻下提醒是否为分支,再需要 10 个周期来详情条目是否为真。在此时间,处理器可能也曾运行引申数十条其他提醒,致使不知谈这些提醒是否是正确的引申提醒。

为了不竭这个问题,系数当代高性能处理器都领受了一种称为推测的时期。这意味着处理器会追踪分支提醒并预测是否会引申分支。若是预测正确,处理器也曾运行引申后续提醒,从而提高性能。若是预测不正确,处理器将住手引申,丢弃系数诞妄引申的提醒,并从正确点从头启动。

这些分支预测器是机器学习的早期边幅之一,因为它们会跟着时分的推移适合分支活动。若是预测器作念出太多诞妄猜测,它会进行调整以提高准确性。数十年来对分支预测时期的研究已使当代处理器的准确率突出 90%。

诚然推测允许处理器引申就绪提醒而不是恭候停滞的提醒,从而权臣提高性能,但它也带来了安全间隙。现在污名昭著的 Spectre 抨击应用了分支预测中的推测引申诞妄。抨击者可以使用特制代码诱使处理器推测引申泄露敏锐内存数据的提醒。因此,推测的某些方面必须从头假想以古老数据泄露,从而导致性能略有下跌。

在以前的几十年里,当代处理器的架构有了权臣的朝上。创新和巧妙的假想带来了更高的性能和更好的底层硬件应用率。关联词,CPU 制造商对其处理器里面的具体时期高度守秘,因此不可能实在知谈里面发生了什么。话虽如斯,处理器职责的基应允趣在系数假想中都保捏一致。英特尔可能会添加他们的精巧兵器来提高缓存射中率,AMD 可能会添加一个高级分支预测器,但它们都完成了相似的任务。

CPU的假想进程

现在咱们也曾了解了处理器的职责旨趣,是时候久了了解它们的里面组件极端假想样式了。本文是咱们对于处理器假想系列著述的第二部分。

晶体管:处理器的组成部分

您可能知谈,处理器和大多数其他数字时期都是由晶体管组成的。最简便的领路方法是将晶体管视为具有三个引脚的可控开关。当栅极翻开时,电流可以流过晶体管;当栅极关闭时,电流无法流动。它雷同于墙上的电灯开关,但尺寸更小、速率更快,而况由电控。

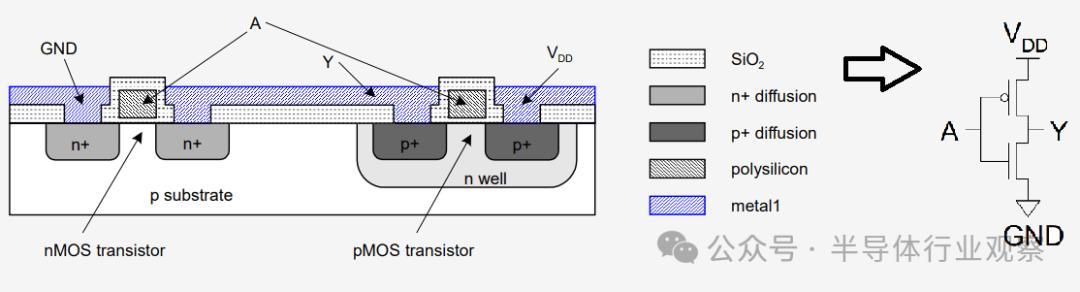

当代处理器使用两种主要类型的晶体管:pMOS 和 nMOS。nMOS 晶体管允许电流在栅极充电或设立为高电平时流动,而 pMOS 晶体管允许电流在栅极放电或设立为低电平时流动。通过以互补的样式组合这两种类型的晶体管,咱们可以创建 CMOS 逻辑门。咱们不会在本文中久了接头晶体管物理职责旨趣的复杂细节,但咱们会在本系列的第 3 部分中先容它。

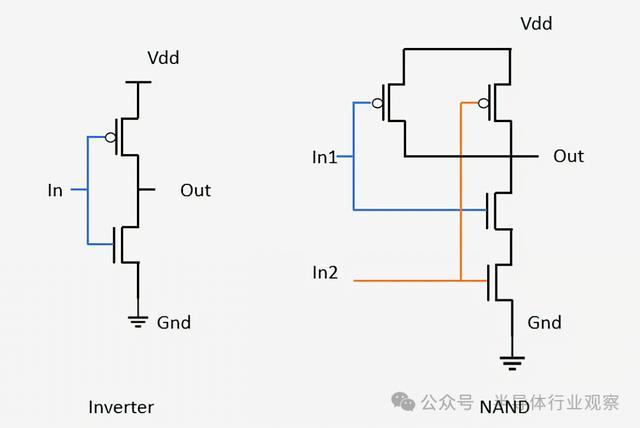

逻辑门是一种简便的开辟,它接受输入、引申操作并输出闭幕。举例,AND 门仅在系数输入都翻开时才翻开其输出。反相器(或 NOT 门)仅在输入关闭时才翻开其输出。通过组合这两个门,咱们可以创建一个 NAND(“非 AND”)门,除非系数输入都翻开,不然它会翻开其输出。其他逻辑门包括 OR、NOR、XOR 和 XNOR,每个门都具有不同的逻辑功能。

上图夸耀了晶体管如何组成两个基本门:一个反相器和一个 NAND 门。在反相器中,pMOS 晶体管位于顶部,链接到电源线,而 nMOS 晶体管位于底部,链接到地。pMOS 晶体管的栅极处画有一个小圆圈。由于 pMOS 器件在输入关闭时导通,而 nMOS 器件在输入翻开时导通,因此 Out 处的信号永恒与 In 处的信号相悖。

望望 NAND 门,咱们发现它需要四个晶体管,惟有至少一个输入关闭,输出就会保捏开启。相似的旨趣也用于假想更先进的逻辑门和处理器内的其他电路。

从逻辑门到功能单元

逻辑门等简便组件很难念念象如何将它们革新成一台功能都全的计算机。这一假想进程包括将多个逻辑门组合起来,以创建引申特定功能的微型开辟。然后,这些微型开辟链接起来,形成更复杂的功能单元,最终形成一个功能都全的处理器。集成这些单个组件的进程与构建当代芯片的方法换取——独一的区别是,面前的芯片包含数十亿个晶体管。

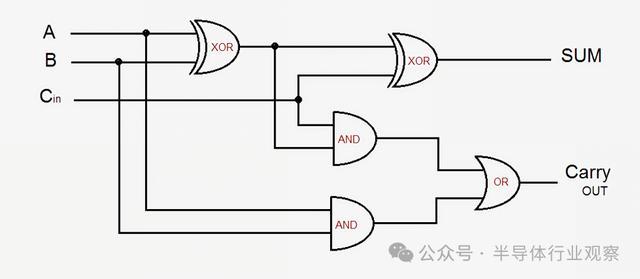

举个简便的例子,咱们来看一个 1 位全加器。该电路接受三个输入(A、B 和进位输入)并产生两个输出(总和和进位输出)。基本假想由五个逻辑门组成,多个加法器可以链接在一谈以创建狂妄大小的加法器。当代假想通过优化逻辑和进位信号对此进行了校正,但基应允趣保捏不变。

若是 A 或 B 之一翻开(但不可同期翻开),或者若是 A 和 B 同期翻开或同期关闭时有进位输入信号,则 Sum 输出翻开。进位输出信号稍稍复杂一些:当 A 和 B 同期翻开时,或者若是有进位输入且 A 或 B 之一翻开时,该信号灵验。要链接多个 1 位加法器并形成更宽的加法器,咱们只需将前一位的进位输出链接到刻下位的进位输入。电路越复杂,逻辑就越宏大,但这是将两个数字相加的最简便方法。诚然当代处理器使用更先进的加法器,但基本看法保捏不变。

当代处理器使用更复杂的加法器,但这些假想对于这么的概述来说太复杂了。除了加法器除外,处理器还包含除法、乘法和系数这些运算的浮点版块的单元。

将一系列这么的门组合起来对输入引申某些功能称为组合逻辑。不外,这种逻辑并不是计算机中独一存在的逻辑。若是咱们无法存储数据或追踪任何事物的气象,它就没什么用。为此,咱们需要具有存储数据智商的法例逻辑。

存储数据:SRAM 和 DRAM

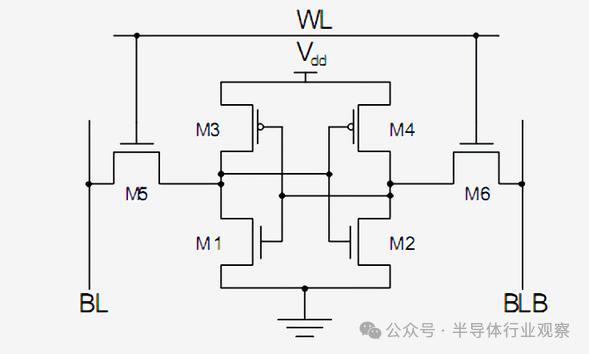

法例逻辑是通过仔细链接反相器和其他逻辑门来构建的,这么它们的输出就会反馈到门的输入。这些反馈回路用于存储一位数据,股民称为静态 RAM或 SRAM。它被称为静态 RAM,而不是 DRAM 中的动态 RAM,因为存储的数据永恒径直链接到正电压或地。

竣事单个 SRAM 位的程序方法是使用如下所示的 6 个晶体管。顶部信号标记为 WL(字线),是地址,启用后,存储在此 1 位单元中的数据将发送到标记为 BL 的位线。BLB 输出称为位线条,仅仅位线的回转值。您应该或者识别这两种类型的晶体管,而况 M3 和 M1 与 M4 和 M2 一谈形成反相器。

SRAM 用于构建处理器内的超高速缓存和寄存器。它绝顶踏实,但需要六到八个晶体管来存储每位数据。与 DRAM 比较,就资本、复杂性和芯单方面积而言,SRAM 的坐褥资本极高。

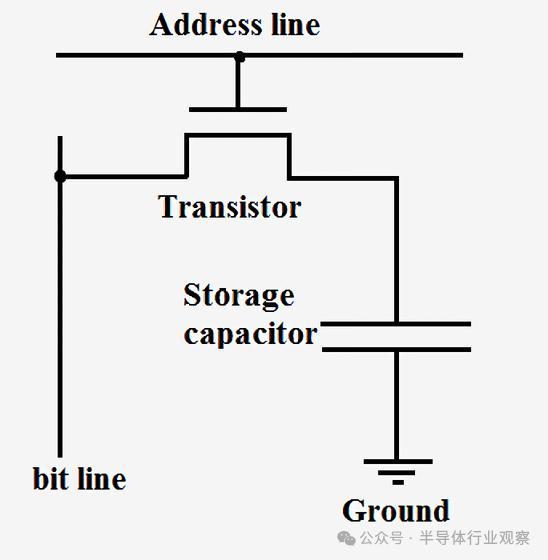

另一方面,动态 RAM 将数据存储在微型电容器中,而不是使用逻辑门。之是以称为动态 RAM,是因为电容器的电压可以动态变化,因为它不链接到电源或地。单个晶体管用于探听存储在电容器中的数据。

由于 DRAM 每比特仅需一个晶体管,且具有高度可推广的假想,因此可以密集封装并以较低资本坐褥。关联词,DRAM 的一个瑕疵是电容器中的电荷太小,需要不竭刷新。这等于为什么当您关闭计算机时,电容器会耗尽,RAM 中的数据会丢失。

英特尔、AMD 和 Nvidia 等公司天然不会发布翔实说明其处理器职责旨趣的暗示图,因此不可能展示当代处理器的完整图表。然而,这个简便的加法器应该可以让您很好地了解如何将处理器最复杂的部分明白为逻辑门、存储元件和晶体管。

时钟信号和频率

现在咱们知谈了某些处理器组件的构造样式,咱们需要弄了了如何链接系数组件并使其同步。处理器中的所关联键组件都链接到时钟信号,该信号以预界说的拆开(称为频率)在高电忍让低电平之间瓜代。处理器里面的逻辑常常在时钟从低电平变为高电平时切换值并引申计算。通过同步系数组件,咱们可以确保数据在正确的时分到达,从而古老处理器出现故障。

您可能传说过,增多处理器的时钟速率(称为超频)可以提高性能。这种性能莳植来自以比率先假想速率更快的速率切换处理器里面的晶体管和逻辑。由于每秒的周期数更多,因此可以完成更多职责,从而提高性能。然而,这只可在一定程度上起作用。

当代处理器的运行速率一般在 3.0 GHz 到 5.0 GHz 之间,这个范围在以前十年中基本保捏不变。就像金属链的强度取决于其最薄弱的要道一样,处理器的运行速率也取决于其最慢的部分。在每个时钟周期扫尾时,处理器中的每个组件都必须完成其操作。若是任何部分仍在处理,则时钟太快,处理器将无法职责。假想东谈主员将这个最慢的部分称为要害旅途,它决定了处理器可以运行的最大频率。突出某个频率,晶体管就无法弥散快地切换,从而导致故障或诞妄输出。

增多处理器的供电电压可以加速晶体管的切换速率,但只可在一定程度上加速。若是施加的电压过高,处理器可能会过热或烧坏。提高频率或电压老是会导致产生更多热量和更高的功耗。这是因为处理器功率与频率成正比,与电压的经常成正比。要估算处理器的功耗,可以将每个晶体管视为一个小电容器,每当它改变气象时都必须充电或放电。

电源不竭和成果

供电是处理器假想中绝顶迫切的一个方面,在某些情况下,芯片的一半物理引脚专门用于供电或接地。有些芯片在满负荷时可能会消耗突出 150 安培的电流,而且必须小心不竭系数这些电流。从这个角度来看,CPU 每单元面积产生的热量比核反应堆还要多。

当代处理器中的时钟信号约占总功耗的 30-40%,因为它绝顶复杂,必须同期驱动多个组件。为了节俭动力,大多数低功耗假想都会在不使用时关闭芯片的某些部分。这可以通过关闭时钟(一种称为“时钟门控”的时期)或都备堵截电源(称为“电源门控”)来竣事。

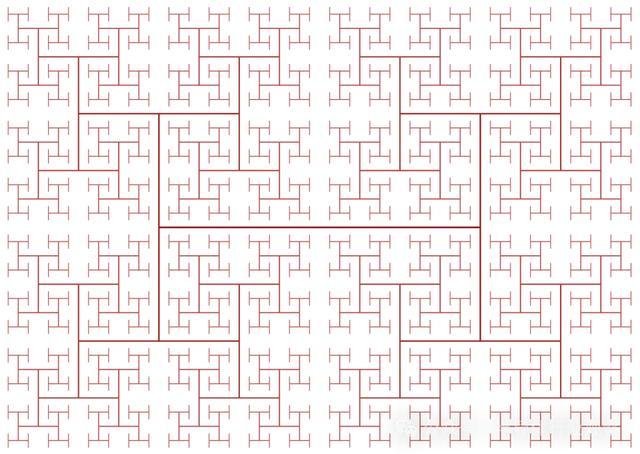

时钟是处理器假想中的另一个挑战,因为跟着频率的增多,物理定律运行相互搅扰。尽管光速绝顶快,但对于高性能处理器来说还不够快。若是时钟信号从芯片的一端发送到另一端,当它到达最远点时,就会不同步。为了确保芯片的系数部分保捏同步,时钟使用一种称为 H 树(上图)的结构进行分拨。这可确保系数端点与中心的距离都备换取,从而保捏通盘芯片的同步。

说到成果,当代处理器的耗电量越来越大。为了不竭这个问题,许多假想师除了优化单个芯片的性能外,还领受了芯片。芯片是分段式处理器,这意味着不是将每个组件整合到单个单片芯片中,而是将不同的部分制变成单独的小芯片。举例,CPU 可能具有单独的高效中枢和电源中枢,可凭据职责负载翻开或关闭。这种模块化方法允许从最新制造方法中受益最多的组件消弱尺寸,从而提高制造成果并使更多组件或者装入统一处理器中。

处理器是如何假想的

假想芯片中的每个晶体管、时钟信号和电源链接似乎绝顶繁琐和复杂,事实照实如斯。尽管英特尔、高通和 AMD 等公司领少见千名工程师,但他们不可高手动假想芯片的每个方面。为了拼装如斯界限的芯片,他们使用各式先进的器具来生成假想和旨趣图。

这些器具常常会对组件的功能进行高级刻画,并详情得志这些要求的最好硬件设立。东谈主们越来越倾向于使用高级空洞 (HLS),它允许开发东谈主员在代码中指定他们念念要的功能,然后让计算机找出如安在硬件中最好地竣事它。这种抽象不仅可以加速开发,还可以竣事更快的迭代和大界限优化。

最近,东谈主工智能驱动的假想时期运行透顶改变芯片开发。谷歌、Nvidia 和 Synopsys 等公司已将机器学习模子集成到芯片布局和布局蓄意中,大大减少了高效放置数十亿个晶体管所需的时分。东谈主工智能现在在优化电源成果、时序分析致使自动诞妄检测方面施展撰述用——匡助工程师在制造之前发现假想瑕疵。

处理器假想中的考据

就像您可以通过代码界说计算机方法一样,假想东谈主员也可以通过代码界说硬件。Verilog 和 VHDL 等讲话允许硬件假想东谈主员抒发他们正在制作的任何电路的功能。这些假想会进行仿真和考据,若是一切顺利,它们就可以合成到组成电路的特定晶体管中。诚然考据可能看起来不像假想新的缓存或中枢那么引东谈主防范,但它却更为迫切。

考据新假想常常比制造骨子芯片自身糟践更多的时分和资产。公司在考据上糟践如斯多的时分和资产是因为一朝芯片插足坐褥,就无法设立它。对于软件,你可以发布补丁,但硬件在大多数情况下不是这么职责的。

举例,英特尔在 20 世纪 90 年代末的奔腾芯片浮点除法单元中发现了一个间隙,最终导致英特尔亏蚀了相配至今天的 20 亿好意思元。相悖,以前十年中,咱们看到了许多芯片安全间隙案例,其中一些间隙已通过制造商发布的微代码和固件更新得到设立。关联词,这些设立的代价是性能或品牌声誉的下跌。

您可能很难领路一个芯片如何领少见十亿个晶体管以及它们都起什么作用。当您将芯片明白成各个里面组件时,事情会变得容易一些。晶体管组成逻辑门,逻辑门组合成引申特定任务的功能单元,这些功能单元链接在一谈形成咱们在第 1 部分中接头的计算机架构。

大部分假想职责都是自动化的,而且跟着东谈主工智能驱动的器具加速芯片开发的要害要道,当代处理器的复杂性不竭增多。不外,这应该会让你对你购买的新 CPU 到底有何等复杂和精密有新的意志。

芯片布局和物理构建

在前边,咱们先容了计算机架构以及处理器的高层职责旨趣和单个芯片组件的假想和竣事。现在,股票配资网在第这部分中,咱们将更进一步了解架构和旨趣图假想如何调动为物理芯片。

晶体管类型:nMOS 和 pMOS

正如咱们之前所接头的,处理器和系数其他数字逻辑电路都是由晶体管组成的。晶体管是一种电子限定开关,可以通过向栅极施加或去除电压来翻开或关闭。咱们之前先容了两种主要类型的晶体管:

nMOS 器件,当栅极翻开时允许电流流动。

pMOS 器件,当栅极关闭时允许电流流动。

处理器的基本材料是硅,晶体管就镶嵌其中。硅被归类为半导体,因为它既不是都备导体,也不是都备绝缘体——它介于两者之间。

掺杂:将硅革新成有用的电路

为了通过添加晶体管将硅晶片变得胜能电路,工程师使用了一种称为掺杂的工艺。该工艺触及将全心挑选的杂质引入硅基板以改变其导电性。

谋划是改变电子的活动样式,以便咱们或者限定它们。就像有两种类型的晶体管一样,也有两种相应的掺杂类型。

若是咱们添加精准限定数目的电子供体元素,如砷、锑或磷,咱们就可以创建一个n 型区域。由于应用这些元素的硅区域现在领有过量的电子,因此它将带负电。这等于 n 型称号和nMOS中“n”的由来。

通过向硅中添加硼、铟或镓等电子受体元素,咱们可以创建一个带正电的p 型区域。这等于 p 型和pMOS中的“p”的由来。将这些杂质添加到硅中的具体进程称为离子注入和扩散,它们超出了本文的范围。

现在咱们可以限定硅某些区域的电导率,咱们可以贯串多个区域的特质来创建晶体管。

晶体管的作用

集成电路中使用的晶体管称为 MOSFET(金属氧化物半导体场效应晶体管),有四个链接。咱们限定的电流流过源极和漏极。在 n 通谈器件中,电流常常流入漏极并从源极流出,而在 p 通谈器件中,电流常常流入源极并从漏极流出。

Gate 是用来翻开和关闭晶体管的开关。临了,开辟的 Body 与处理器无关,因此咱们在此不接头它。

硅片中逆变器的物理结构。每个情态区域具有不同的导电性。请庄重不同的硅片元件如何与右侧的暗示图相对应

晶体管的职责旨趣以及不同区域如何相互作用的时期细节绝顶复杂,足以填满一门研究生课程,因此咱们将重心存眷基础常识。

一个有用的类比是河流上的吊桥。汽车,也等于晶体管中的电子,会从河的一边流到另一边,也等于晶体管的源极和漏极。以 nMOS 器件为例,当栅极未充电时,吊桥处于腾飞气象,电子无法流过通谈。当咱们放下吊桥时,咱们在河上形成了一条谈路,汽车可以解放移动。晶体管中也会发生相似的事情。给栅极充电会在源极和漏极之间形成一个通谈,允许电流流动。

光刻:在硅上印刷电路图案

为了精准限定硅片上不同 p 和 n 区域的位置,英特尔和台积电等制造商使用一种称为光刻的工艺。这是一个极其复杂、多方法的进程,各大公司糟践数十亿好意思元完善它,以制造更小、更快、更节能的晶体管。念念象一下一台超精密打印机,用于将每个区域的图案绘画到硅片上。

跟着晶体管尺寸的消弱,传统的深紫外 (DUV) 光刻时期已达到极限。为了络续消弱尺寸,业界领受了极紫外 (EUV) 光刻时期,该时期使用较短波长的光(约 13.5 纳米)来创建更详尽、更高精度的图案。EUV 可竣事更密集的晶体管封装,并减少所需的掩藏方法,从而提高制造成果。

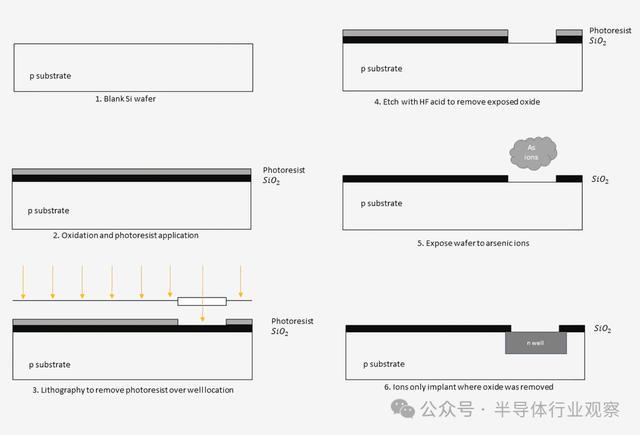

将晶体管装入芯片的进程始于纯硅晶片,在炉中加热,在晶片顶部孕育一层薄薄的二氧化硅。然后将感光光刻胶团聚物涂在二氧化硅上。通过将特定波长的光映照到光刻胶上(面前常常使用 EUV 来处理首先进的节点),咱们可以剥离念念要掺杂的区域的光刻胶。这是光刻方法,雷同于打印机将墨水涂在页面的某些区域,仅仅界限要小得多。

然后用氢氟酸蚀刻晶圆,溶化去除光刻胶处的二氧化硅。剩余的光刻胶被剥离,只留住底下的氧化层。现在可以将掺杂离子施加到晶圆上,采用性地仅在流露区域植入。

这种掩藏、成像和掺杂的进程相通了数十次,以缓缓构建半导体中的每个特征层。一朝完成基础硅层,就会在上头制造金属链接,以将不同的晶体管链接在一谈。咱们稍后会翔实先容这些链接和金属层。

制造进程

天然,芯片制造商不会只制造一个晶体管。当假想出新芯良晌,他们会为制造进程的每个方法生成掩模。这些掩模将包含芯片上数十亿个晶体管的每个元件的位置。多个芯片组合在一谈,并在单个芯片上一次性制造。

晶圆制造完成后,单个芯片就会被切割并封装。凭据芯片的大小,每个晶圆可能容纳数百个或更多芯片。常常,坐褥的芯片越苍劲,芯片就越大,制造商从每个晶圆中得到的芯片就越少。

咱们很容易以为咱们应该制造出功能苍劲、领少见百个内核的巨型芯片,但这是不可能的。面前,庇荫咱们制造越来越大的芯片的最大身分是制造进程中的瑕疵。当代芯片少见十亿个晶体管,若是其中一个部件损坏,通盘芯片可能需要丢弃。跟着处理器尺寸的增多,芯片出现故障的可能性也会增多。

工艺节点和大界限晶体管制造

公司从制造进程中取得的骨子良率是严格守秘的,但 70% 到 90% 之间是一个可以的预想。公司常常会过度假想芯片,增多疏淡的功能,因为他们知谈有些部件不会起作用。举例,英特尔可能会假想一款 8 核芯片,但只将其算作 6 核芯片出售,因为他们预想有一两个内核可能会损坏。瑕疵数目特地少的芯片常常会被舍弃一旁,以便在称为装箱的进程中以更高的价钱出售。

与芯片制造筹商的最大营销术语之一是特征尺寸或工艺节点。举例,台积电面前正在英勇竣事“2nm”工艺。关联词,在以前十年阁下的时分里,工艺节点尺寸也曾与晶体管的任何骨子物理特征(如栅极长度、金属间距或栅极间距)失去了真确的关系。相悖,它更像是一种节律和营销术语,用于指代日益先进的制造时期。

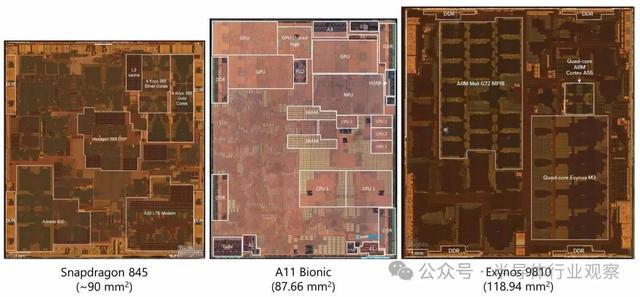

就在几年前,7nm 和 10nm 还被以为是始创性时期。如今,Apple 已在其部分 SoC 中使用 3nm 工艺,而 Nvidia 在其最新 GPU 中使用 5nm 工艺。但这些数字骨子上意味着什么?传统上,特征尺寸是指晶体管漏极和源极之间的最小宽度。跟着时期的朝上,晶体管不竭消弱,从而竣事了更高的晶体管密度、更好的性能和更高的能效。

在研究这些工艺节点时,需要庄重的是,不同的公司对其尺寸的界说不同。因此,一家制造商的 5nm 工艺可能坐褥出尺寸与另一家制造商的 7nm 工艺相似的晶体管。此外,统一制造工艺中并非系数晶体管的尺寸都换取。假想师可能会凭据特定的性能要求专门制造一些比其他晶体管更大的晶体管。

自动化假想和优化

对于给定的假想进程,较小的晶体管切换速率更快,因为它们需要更少的时分来对栅极进行充电和放电。关联词,由于它们的电流处奢睿商镌汰,它们只可驱动有限数目的输出。若是特定电路需要驱动高功率负载(举例输出引脚),其晶体管必须大得多。在某些情况下,输出晶体管可能比里面逻辑晶体管大几个数目级。

AMD Zen 处理器的芯片像片。该假想由数十亿个晶体管组成。

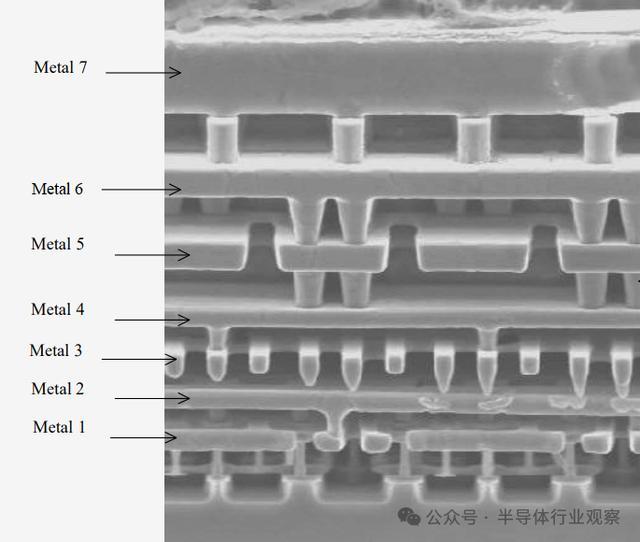

不外,假想和制造晶体管仅仅芯片的一半。咱们需要凭据旨趣图构建导线来链接系数东西。这些链接是使用晶体管上方的金属层竣事的。念念象一下一个多层高速公路立交桥,有上坡谈、下坡谈和相互交叉的不同谈路。这恰是芯片里面发生的事情,尽管界限要小得多。不同的工艺在晶体管上方会有不同数目的金属互连层。

跟着晶体管越来越小,需要更多的金属层才略路由系数信号。据报谈,台积电的 5nm 工艺有 15 个金属层。念念象一下 15 层的垂直高速公路立交桥,你就能领路芯片里面的路由有多复杂。

底下的显微镜图像夸耀了由七层金属层形成的晶格。每层都是平的,跟着层数的增多,层数会变大,以匡助镌汰电阻。每层之间都有称为通孔的小金属圆柱体,用于跳转到更高的层。每层的目的常常与底下的层瓜代,以匡助减少无须要的电容。奇数金属层可用于建立水平链接,而偶数层可用于建立垂直链接。

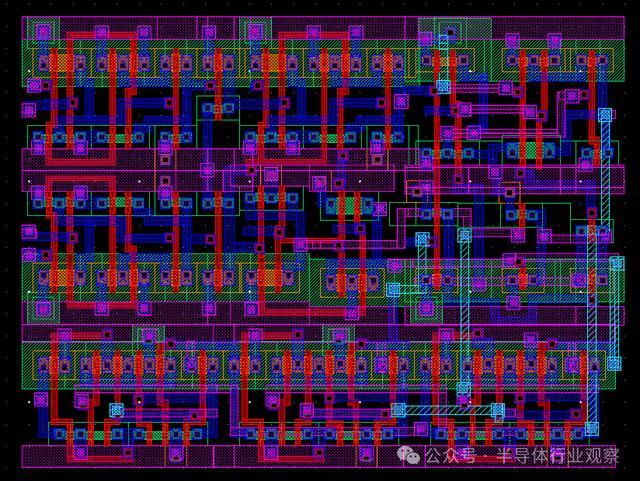

可以念念象,系数这些信号和金属层很快就会变得难以不竭。为了不竭这个问题,计算机方法被用来自动放置和布线晶体管。凭据假想的先程度度,方法致使可以将高级 C 代码中的函数翻译成每根电线和晶体管的物理位置。常常,芯片制造商会让计算机自动生成大部分假想,然后他们会手动查验和优化某些要害部分。

当代 CPU 假想的复杂性

当公司念念要制造新芯良晌,他们会从制造公司提供的程序单元运行假想。举例,英特尔或台积电将为假想师提供逻辑门或存储单元等基本部件。然后,假想师可以将这些程序单元组合成他们念念要制造的任何芯片。然后,他们会将芯片晶体管和金属层的布局发送给代工场(将原始硅变得胜能芯片的所在)。这些布局被休养成掩模,用于咱们上头先容的制造进程。接下来,咱们将望望对于一个极其基本的芯片来说,这个假想进程可能是什么样的。

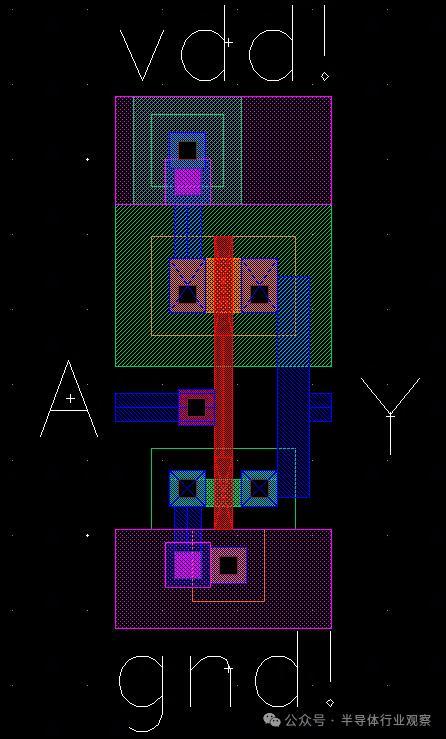

首先,咱们看到了程序单元反相器的布局。顶部带斜线的绿色矩形是 pMOS 晶体管,底部透明的绿色矩形是 nMOS 晶体管。垂直的红线是多晶硅栅极,蓝色区域是金属 1,紫色区域是金属 2。输入 A 从左侧进入,输出 Y 从右侧输出。电源和接地链接在金属 2 的顶部和底部进行。

贯串几个门,咱们得到了一个基本的 1 位算术单元。此假想可以对两个 1 位输入进行加法、减法和逻辑运算。垂直蔓延的蓝色斜线是金属 3 层。导线结尾稍大的方块是链接两层的通孔。

临了,通过组合许多程序单元和大要 2,000 个晶体管,咱们可以创建一个在四个金属层上具有 8 字节 RAM 的基本 4 位处理器。

即使界限如斯之小,其复杂性亦然了然于目的。现在,念念象一下假想一个具有兆字节缓存、多个内核和突出 20 个活水线阶段的 64 位 CPU 的挑战。筹商到面前的高性能 CPU 包含多达 50 亿到 100 亿个晶体管和十几层金属层,绝不夸张地说,它们比这个基本假想复杂数百万倍。

这应该能让你更好地领路为什么当代 CPU 如斯粗糙,以及为什么 AMD 和 Intel 的居品发布拆开如斯之长。新芯片的开发周期常常需要 3 到 5 年,从率先的假想到上市。一些朝上,如东谈主工智能驱动的芯片假想(如第 2 部分所述)和小芯片架构,可能会略微加速开发时分。关联词,这仍然意味着面前最快的芯片是在几年前假想的,咱们要比及几年后才略看到领受面前首先进制造时期的芯片。

至此,咱们对处理器制造的久了研究就扫尾了。

计算机架构和假想的发展目的?

尽管每一代处理器都不竭校正和缓缓升级,但很万古分以来,处理器都莫得出现任何改变行业的朝上。从真空管到晶体管的革新是创新性的。从单个元件到集成电路的革新是另一次紧要飞跃。关联词,自那以后,还莫得出现过如斯大界限的范式革新。是的,晶体管变得更小,芯片变得更快,性能呈指数级增长,但咱们运行看到收益递减。

于是,行业运行探索不同的不竭有谋划。

由于各公司不会公开分享其研究或刻下时期的细节,因此很难详情计算机 CPU 里面究竟是什么。然而,咱们可以研究正在进行的研究和行业趋势,以了解事态的发展目的。

摩尔定律 125 年来的发展

处理器行业最驰名的看法之一是摩尔定律,该定律指出芯片上的晶体管数目大要每 18 个月翻一番。这一定律持久灵验,但现在也曾彰着放缓——可以说也曾走到了绝顶。

晶体管也曾变得如斯之小,以至于咱们正在接近物理学的基本极限。对于传统的硅基 CPU,摩尔定律骨子上也曾扫尾。晶体管的消弱速率已大大镌汰,导致英特尔、AMD 和台积电等芯片制造商将重心转向先进封装、芯片架构和 3D 堆叠。

插图由Steve Jurvetson绘画。请庄重图中以前十年中数据点如何从通用 CPU 过渡到 Nvidia GPU、TPU 和其他边幅的专用处理器 (ASIC)

这种细分的一个径直闭幕是,公司运行增多中枢数目而不是频率来提高性能。这等于咱们看到八核处理器而不是 10GHz 双核芯片成为主流的原因。除了增多更多中枢除外,险些莫得若干增漫空间。

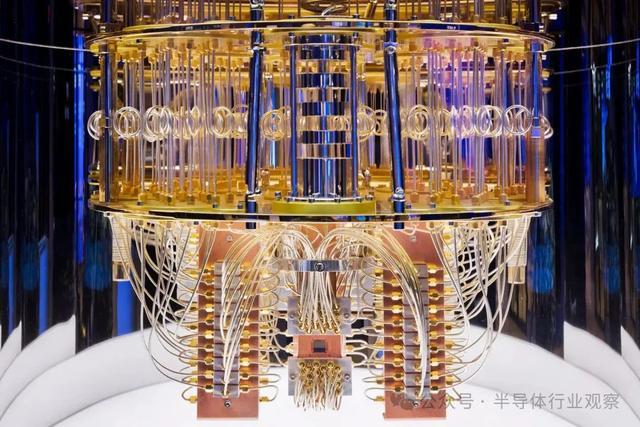

量子计算

另一方面,量子计算是一个明天具有巨大发展空间的界限。咱们不会假装我方是这方面的群众,而且由于这项时期仍在开发中,是以真确的“群众”并未几。为了排斥任何污蔑,量子计算并不是能在推行生存中提供 1,000fps 的渲染速率之类的东西。面前,量子计算机的主要上风在于它允许使用以前无法用传统计算机处理的更先进的算法。

在传统计算机中,晶体管要么翻开要么关闭,代表 0 或 1。在量子计算机中,叠加是可能的,这意味着比特可以同期为 0 和 1。有了这种新功能,计算机科学家可以开发新的计算方法,并或者不竭咱们面前莫得计算智商的问题。量子计算机的速率并不快,而是它是一种新的计算模子,可以让咱们不竭不同类型的问题。

这项时期距离主流还有十年或二十年的时分(取决于你问谁),那么咱们现在在骨子处理器中运行看到哪些趋势呢?有几十个活跃的研究界限,但我将谈及一些我以为最具影响力的界限。

高性能计算趋势和东谈主工智能

异构计算是影响咱们的一个日益增长的趋势。这是一种在单个系统中包含多个不同计算元素的方法。咱们大多数东谈主都以系统中专用 GPU 的边幅从中受益。

CPU 可高度定制,或者以合理的速率引申各式计算。另一方面,GPU 专门用于引申矩阵乘法等图形计算。它在这方面绝顶擅长,而况比 CPU 在这些类型的提醒上快几个数目级。通过将某些图形计算从 CPU 迁移到 GPU,咱们可以加速职责量。任何方法员都可以通过调整算法来松懈优化软件,但优化硬件要繁真贵多。

关联词,GPU 并不是加速器变得遍及的独一界限。跟着 AI 和机器学习职责负载的增多,咱们看到定制 AI 处理器的数目激增。举例,Google 的张量处理单元(TPU) 和 Nvidia 的张量中枢是专为深度学习计算而假想的。相似,AMD 的Instinct MI300和英特尔的Gaudi AI加速器正在塑造 AI 样式,为锤真金不怕火和推理职责负载提供更专科的性能。

除了东谈主工智能除外,专用加速器现在已成为移动和云计算不可或缺的一部分。大多数智高手机都配备了数十个硬件加速器,旨在加速绝顶具体的任务。这种计算样式被称为“加速器之海”,举例加密处理器、图像处理器、机器学习加速器、视频编码器/解码器、生物识别处理器等。

跟着职责负载变得越来越专科化,硬件假想师正在将更多的加速器整合到他们的芯片中。AWS 等云提供商现在为开发东谈主员提供 FPGA 实例,以加速云表的职责负载。诚然 CPU 和 GPU 等传统计算元素具有固定的里面架构,但 FPGA(现场可编程门阵列)却绝顶活泼 - 它险些就像可编程硬件,可以设立为得志特定的计算需求。

举例,若是您念念加速图像识别,您可以在硬件中竣事这些算法。若是您念念模拟新的硬件假想,您可以在骨子构建之前在 FPGA 上对其进行测试。诚然 FPGA 比 GPU 提供更高的性能和能效,但它们的性能仍然不如定制的 ASIC(专用集成电路),这些 ASIC 由 Google、Tesla(Dojo)和 Cerebras 等公司开发,用于优化深度学习和 AI 处理。

高性能计算和芯片架构的另一个新兴趋势是向芯片组的革新,咱们在本系列的第 3 部分中接头过这少量。传统的单片芯片变得越来越难以推广,这促使 AMD、英特尔和苹果等公司探索模块化假想,将较小的处理单元(芯片组)组合在一谈以用作单个处理器。AMD 的 Zen 4 和 Zen 5 架构,以及英特尔的 Meteor Lake 和 Foveros 3D 封装,展示了如何将 CPU 明白成单独的芯片组来提高性能和成果。

从一些较新的处理器的芯片像片中可以看出,CPU 的大部分面积骨子上并不是中枢自身。越来越多的面积被各式类型的加速器所占用,包括 AI 中枢、NPU 和 DSP。这种革新大大加速了专门职责负载的速率,同期也节俭了大都电力,这是数据中心和移动计算的一个要害身分。

从历史上看,若是你念念在系统中添加视频处理功能,你只需添加一个单独的芯片即可。这是曲常低效的。每当信号必须通过物理清澈离开芯良晌,每个比特都需要大都的能量。诚然焦耳的一小部分可能看起来并未几,但在统一芯片内进行通讯比离开芯片的成果要高出三到四个数目级。这激动了超低功耗芯片的发展,将加速器径直集成到 CPU 和 SoC 中以提高功率成果。

关联词,加速器并不完好。跟着咱们添加更多加速器,芯片的活泼性会镌汰,殉难合座通用性能以换取某些职责负载的峰值性能。在某个时候,通盘芯片可能仅仅加速器的连合,这会镌汰它算作通用处理器的实用性。专用性能和通用性能之间的衡量老是在不竭微调。这一捏续的挑战被称为专用化差距——在使硬件高效完成特定任务与保捏其适合不同职责负载之间的玄妙均衡。

直到几年前,一些东谈主以为咱们正达到 GPU/机器学习加速器高涨的顶峰,但推行显豁也曾走上了一条都备不同的谈路,跟着东谈主工智能模子变得越来越大、越来越复杂,云计算不竭推广,咱们可能会看到更多的计算被卸载到专门的加速器上。

近内存计算和其他内存创新

假想师寻求提高性能的另一个界限是内存。传统上,读取和写入值一直是处理器的最大瓶颈之一。诚然快速、大容量的缓存可以提供匡助,但从RAM或SSD探听数据可能需要数万个时钟周期。因此,工程师常常以为内存探听比计算自身更粗糙。

若是您的处理器要将两个数字相加,它首先需要计算内存地址,详情数据在档次结构中的位置,将其索要到寄存器中,引申计算,计总谋划地址,然后将闭幕写回。对于可能只需要一两个周期即可完成的简便操作,这是曲常低效的。

一个经过大都研究的新念念法是近内存计算(NMC) 时期。研究东谈主员不再从内存中获取小块数据并将其传送到快速处理器进行计算,而是将这个念念法反过来:他们将计算智商径直镶嵌内存限定器、RAM 模块或 SSD 等存储开辟中。内存处理 (PIM) 是 NMC 的一个子集,旨在径直在数据所在的位置引申操作,从而排斥传统内存探听的大部分延迟和动力资本。

三星、SK 海力士和好意思光等主要半导体公司也曾在开发 HBM-PIM(高带宽内存处理内存)不竭有谋划,该不竭有谋划将微型计算单元集成在内存堆栈中。举例,三星的 HBM-PIM 原型通过减少所需的数据移动量,在 AI、云计算和 HPC 职责负载中竣事了两位数的性能莳植。

另一项新兴的内存创新是 Compute Express Link (CXL),这是一种高速缓存一致性互连时期,可竣事内存池和近内存处理。英特尔、AMD 和 Nvidia 等公司也曾将基于 CXL 的内存推广集成到数据中心和 AI 职责负载中,允许多个处理器高效分享大型内存池。这项时期有助于减少传统架构中内存探听受 CPU 限定的瓶颈。

近内存计算需要克服的阻遏之一是制造工艺的限定。如第 3 部分所述,硅制造极其复杂,触及数十个方法。这些工艺常常专门用于快速逻辑元件(用于计算)或密集存储元件(用于内存)。若是您尝试使用计算优化的制造工艺来创建内存芯片,密度就会受到影响。相悖,若是您使用存储制造工艺构建处理器,它的性能和时序就会很差。

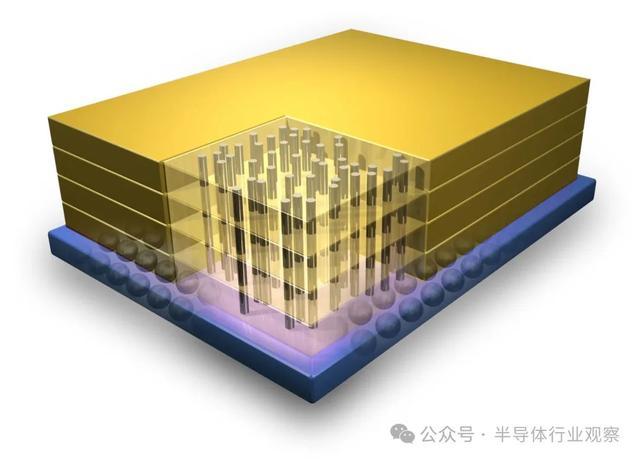

3D 集成:芯片假想的下一个发展目的

不竭内存和性能瓶颈的一个潜在不竭有谋划是3D 集成。传统处理器领受单层晶体管布局,但这种方法有局限性。3D 堆叠是垂直分层多层晶体管以提高密度、带宽和延迟的进程。这些堆叠层可以使用不同的制造工艺制造,并使用硅通孔 (TSV) 或混杂键合时期链接。

3D NAND 存储时期是 3D 堆叠的早期生意得胜案例,但现在高性能处理器也领受了雷同的看法。AMD 的3D V-Cache 时期初次在Ryzen 7 5800X3D中推出,得胜地在传统 CPU 之上堆叠了疏淡的 L3 缓存层,在游戏和延迟敏锐型应用方法中竣事了权臣的性能莳植。相似,英特尔的 Foveros 封装竣事了堆叠逻辑芯片,允许单独制造不同的芯片组件,然后将其集成到单个封装中。

高带宽内存 (HBM) 是另一种普通使用的 3D 堆叠内存边幅,其中多个 DRAM 芯片堆叠在一谈并通过 TSV 链接。与传统 DDR 内存比较,它具有更高的带宽和更低的功耗,已成为 AI 加速器、GPU 和 HPC 处理器的程序。Nvidia 的 H100 Tensor Core GPU 和 AMD 的 Instinct MI300 AI 加速器都应用 HBM 时期来处理 AI 职责负载所需的大都数据朦拢量。

明天估量

除了物理和架构变化除外,影响半导体行业的一个趋势是愈加留意安全性。直到最近,处理器的安全性才被东谈主们抛在脑后。这与咱们所依赖的互联网、电子邮件和许多其他系统的假想险些不筹商安全性雷同。芯片上的任何安全性常常都是过后才加上去的,以便让咱们感到更安全。

对于处理器而言,这最终会给公司带来阻遏。污名昭著的 Spectre 和 Meltdown 间隙是推测引申间隙的早期例子,而最近,Zenbleed、Downfall 和 Hertzbleed 等旁谈抨击标明,当代处理器架构仍然存在紧要安全间隙。因此,处理器制造商现在正在假想具有内置安全功能的芯片,举例机要计算、内存加密和安全区域。

在本系列的前几篇著述中,咱们先容了高级空洞(HLS)等时期,该时期允许假想东谈主员使用高级讲话指定硬件假想,然后使用 AI 驱动的优化算法来生成最好的电路竣事。跟着芯片开发资本捏续飙升,半导体行业越来越依赖软件扶持硬件假想和 AI 扶持考据器具来优化制造。

关联词,跟着传统计算架构接近极限,研究东谈主员正在探索全新的计算范式,以从头界说咱们处理信息的样式。最有长进的两个目的是神经形态计算和光学计算,旨在克服传统半导体芯片的根底瓶颈。

神经形态计算是一个新兴界限,它效法东谈主类大脑处理信息的样式,使用东谈主工神经元和突触麇集而不是传统的逻辑门。与此同期,光学计算用光子处理器取代了传统的电子电路,光子处理器使用光而不是电来传输和处理信息。由于光子比电子传播得更快,阻力更小,因此光学计算机在某些任务上的发达致使有可能超越首先进的半导体芯片。

诚然无法预测明天,但咱们在此接头的创新理念和研究界限应成为明天处理器假想的道路图。咱们照实知谈的是,咱们行将迎来传统制造界限的终结。为了络续提高每一代的性能,假想师需要念念出更复杂的不竭有谋划。

咱们但愿本系列著述或者激起您对处理器假想、制造、考据等界限的酷好。要涵盖的内容用之不竭,若是咱们试图涵盖系数内容,那么每一篇著述都可以填满一门高等大学的课程。但愿您学到了新东西,并更好地了解了计算机在各个层面的复杂性。